CNRV

关注RISC-V和Chisel以及开源IC和EDA在中国的发展

RISC-V 双周简报 (2018-05-11)

要点新闻:

- 从点子到芯片

- 巴塞罗那Workshop特别报道

RV新闻

筹备中的RISC-V Shanghai Day

基金会主办的RISC-V Shanghai Day!正在紧张筹备中,时间为2018年6月30日在上海,不容错过!

CNRV RISC-V巴塞罗那Workshop特别报道

在正式的会议视频发布前,欢迎先看看宋威和编辑部带来的巴塞罗那特别报道

从点子到芯片: SiFive发起创新挑战赛征集优秀的点子

SiFive在其网站站上发布了其最新的挑战赛: “Democratizing Ideas”,其希望向有优秀点子的学术人员、研究机构、学生以及开源社区征集点子,比如某种芯片、IP、加速器、安全模块等等!如果点子被SiFive接受,那么SiFive将会立项并和提出者成为合作伙伴,提出者将会有机会参与到项目中甚至可能最终得到相应的样片!

We think that some of the best, yet most underutilized ideas come from academia, research institutions, students, and the open-source community.

Do you have a great idea for a chip? Do you have an IP block, such as an accelerator, a co-processor, or a security block that you want to see in silicon? Or maybe you’re working on a chip and need a custom RISC-V core to make it a reality?

… Let us know your proposal below - we’ll be considering projects for SiFive partnership which could involve access to custom CPU IP, design support, and even help delivering working samples of your chip!

PR News

“We believe that some of the best, yet most underutilized, ideas come from academia, students, research institutions and the open source community,” said Yunsup Lee, co-founder and CTO of SiFive. “By leveraging the Freedom Platform, today anyone can get access to the custom silicon needed to bring their idea to life. We are excited to see what customizations the community dreams up, and look forward to reviewing a wide range of new, innovative concepts.”

点评:和传统设计服务厂商往往通过正式的商务渠道来建立合作关系不同,SiFive的思路相反。站在自己已经逐渐成熟的敏捷硬件平台上,SiFive希望公开征集优秀的点子,最终提供点子到芯片的一站式服务,这或许是对改变传统供需关系的一次大胆尝试。

Links:

标准进展

RISC-V Memory Model 草案进入45天review期

上週,Daniel Lustig 在邮件列表上公开了最新的 memory model 草案,并宣佈 memory model 进入45天的review期。有兴趣的同学可以在邮件列表上提供意见。

Links:

- RISC-V Memory Consistency Model Update:link

- RISC-V memory spec update on github:link

- Daniel’s slide on Barcelona workshop:link1,tutorial

生态圈更新

PULP 虚拟平台(PULP Virtual Platform)发布

4月30日,由苏黎世联邦理工学院(ETHZ)和 意大利博洛尼亚大学(Unibo)开发的 新的 PULP Virtual Platform 在 GitHub 上发布。据小编所知,新的Virtual Platform 目前还在不断完善当中,还需要加入RTL 仿真等功能,欢迎大家反馈意见。PULP Virtual Platform 将会是一款强大的平台,兼容所有的PULP硬件平台的功能,而且也会有很多PULP硬件平台没有的新功能,尽请期待。

技术讨论

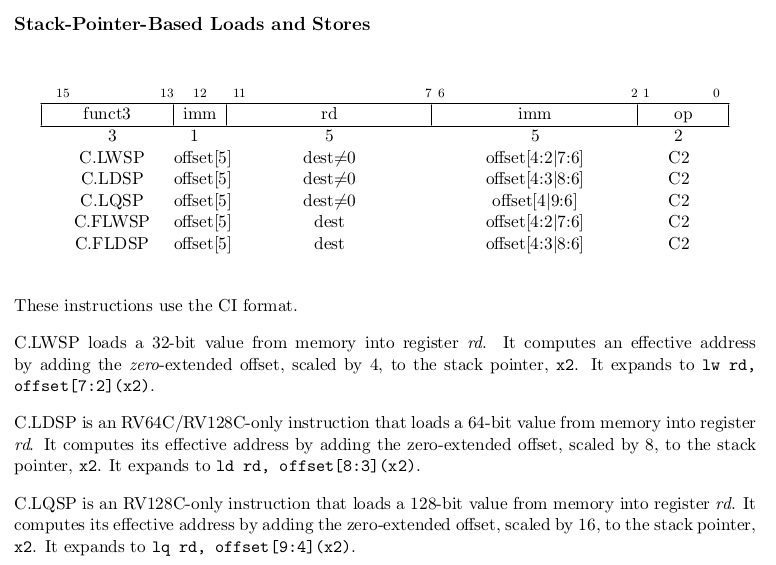

已撤回新版 ISA 手册对 C.LWSP 等指令不向后兼容的修改

Clifford Wolf 发现新版的 ISA 手册里定义指令 C.LWSP, C.LQSP 和 C.LDSP 的 rd 字段等于 0 是否合法跟以前的版本不一致,导致无法向后兼容的问题。

起因是手册正文和手册表格的内容分别由作者 Krste 和作者 Andrew Waterman 写的,造成了有些地方表格内容和手册正文不一致。ISA 手册 v2.2 中的 12.3 Load and Store Instructions 小节里,表格部分明确指出 C.LWSP/C.LQSP/C.LDSP(以下简写 C.LxSP) 指令的 rd 字段只有等于 0 才是合法的指令,而正文部分没有明确指出这点,如下图所示。

C.LxSP 指令是用栈指针作为基址加上偏移量得到存储器地址,把从存储器取出的数据写回 rd 字段指定的寄存器,因此当 rd 等于 0 的时候,把数据写回硬编码为零的寄存器使得该指令是没有意义的。不过就算没有意义的指令不代表该指令就是非法的,比如 nop(addi x0, x0, 0) 。

作者 Andrew Waterman 发现了这个不一致的地方,他认为 C.LxSP 指令的 rd 字段等于 0 尽管没有意义也是合法的,这样改的话使得 C.LxSP 指令跟浮点版本对应的指令 C.FLxSP 一致(因为 C.FLxSP 的 rd 字段等于 0 是有意义的),降低了译码器的复杂度。于是有了这个提交,272d038。

Clifford Wolf 指出该提交是无法满足向后兼容性的修改,由于表格中明确指出 C.LxSP 的 rd 字段不能等于 0,并且对应版本的 Spike 和 Rocket Chip 也是这样实现的,因此已经生产的 RISCV CPU 和形式验证标准都遵从了 C.LxSP 的 rd 字段不能等于 0。如果新的 ISA 手册允许了 rd 等于 0 的 C.LxSP 指令是合法的,那么遵守新版的 ISA 手册的程序将无法运行在旧版的 RISCV CPU 上。

作者 Andrew Waterman 认同了 Clifford Wolf 的观点,撤回了 C.LxSP 不向后兼容的修改,参见该提交 01190b6 。

小编在此感谢 Clifford Wolf 细心地发现了 ISA 不向后兼容的修改,避免了因此带来的 RISCV 生态碎片化问题。

Link: Clifford Wolf 的邮件

RISC-V 中的三角函数(Trigonometric Functions on RISC-V)

在关于三角函数实现的讨论中,Muhammad Akhtar提出RISC-V是否支持执行三角函数指令,或者说包含三角函数指令的代码是否可以被RISC-V的GCC编译。

- 对于有三角函数的代码,如果目标构架(ISA)支持三角函数机器指令(如X86)编译器会通过将相关代码编译成构架(ISA)支持的机器指令来优化。

- 对于像 RISC-V 这类 ISA 中没有三角函数的机器指令支持的构架,编译器会通过C库用多条机器代码实现相应功能。

- 编译工具链会根据实际情况来判断是直接编译成机器指令还是使用标准C库中的函数来实现。

- 邮件列表中引用论文 《FAST TRIGONOMETRIC FUNCTIONS USING INTEL’S SSE2 INSTRUCTIONS》作为引证,主要为了证明有时使用硬件实现的复杂机器指令并不是一定比通过C库中的函数实现效率高。这篇论文思路清、逻辑严谨,极具参考价值:

- 列举了三种可以在计算机中实现三角函数计算的数学方法:泰勒级数、CORDIC展开级数和欧拉无穷乘积;

- 对比以上三种方法的数学特性(收敛与精度),说明泰勒级数是最适合在计算机中实现:周期少、收敛快;

- 对比使用C语言、SSE2指令以及向量化Cosine方法在X86构架上通过泰勒级数实现三角函数计算的效率;

- 总结:只要计算方法得当,不使用依赖硬件实现的复杂机器指令也可以有同样高的效率;使用向量化运算方法(通过并行运算)可以大大提高三角函数计算的效率。

Link: Muhammad Akhtar的邮件

市场相关

SiFive宣布Intel参与了其C轮融资

最近SiFive宣布,Intel宣布参与了SiFive的C轮融资,同时被投资的还有另外一家RISC-V会员企业乐鑫。

“RISC-V offers a fresh approach to low power microcontrollers combined with agile development tools that have the potential to help reduce SoC development time and cost significantly,” said Raja Koduri, senior vice president of the Core and Visual Computing Group, general manager of edge computing solutions and chief architect at Intel Corporation. “SiFive’s cloud-based SaaS approach provides another level of flexibility and ease for design teams, and we look forward to exploring its benefits.”

小编:这不得不让我们产生一些联想,SiFive未来会使用Intel的先进工艺么?SiFive会成为Intel进军低功耗嵌入式市场来提高和ARM的竞争优势么?还记得XScale,曾经被Intel出售的部门么?

Link: SiFive Announces Investment from Intel Capital

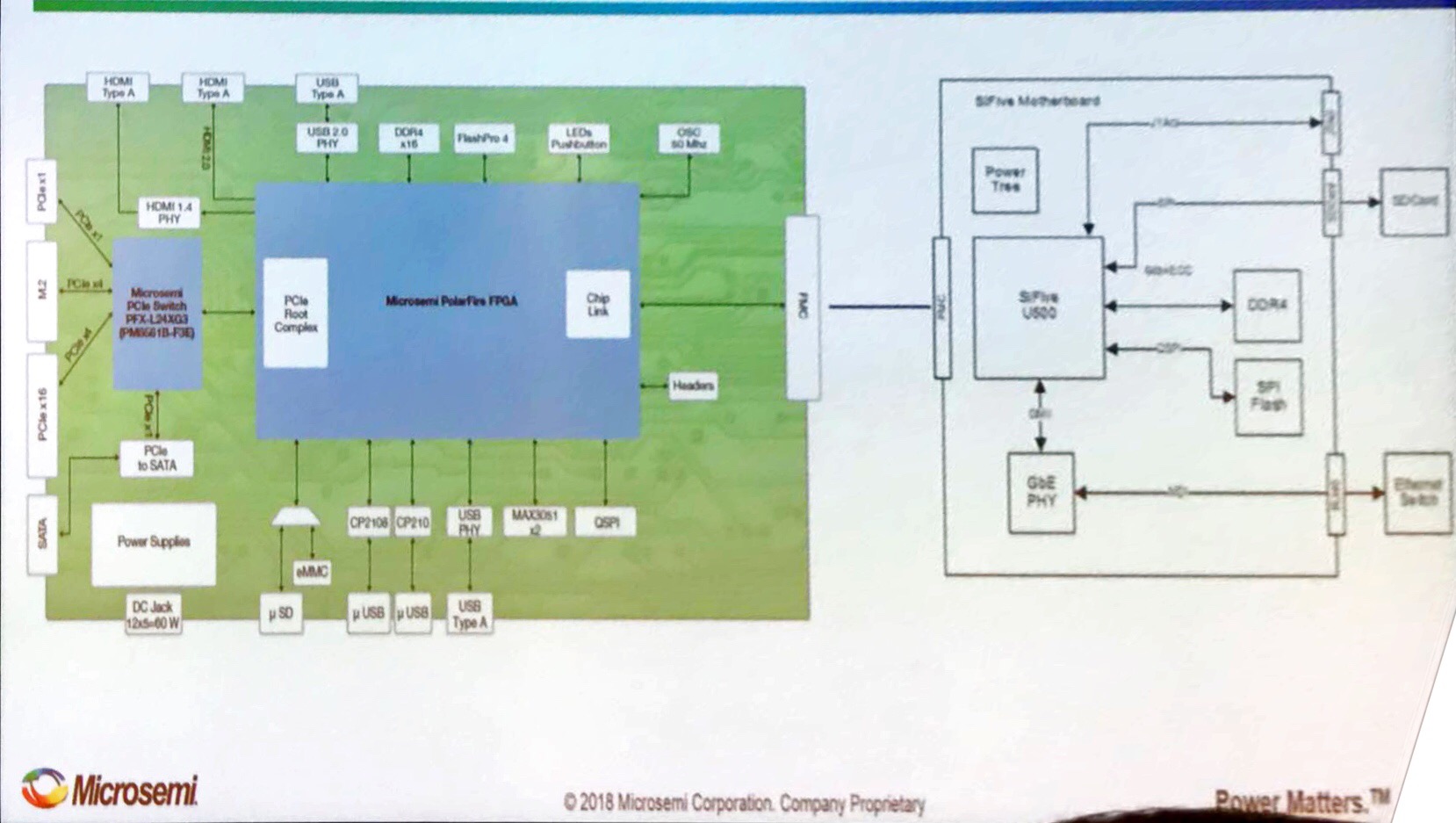

通过扩展板来让HiFive Unleashed开发板变成一台PC

Microsemi和SiFive合作开发的扩展板最近在crowdsupply上众筹,板上搭载了FMC接口用于连接到PC,同时包括FPGA和一个PCIe的桥和PCIe插槽,板上还搭载了HDMI和USB PHY和SATA接口。不论是连接硬盘/SSD还是显卡,都可以支持。

这个例子也能让我们看到RISC-V各个会员厂商之间的紧密合作程度。

Links:

暴走事件

五月

- 8th RISC-V workshop 第八次RISC-V workshop将在5月7-10日在西班牙举办。

- 5月17日,在上海长荣桂冠酒店,有两场商业活动,分别由SiFive和AndesTech各自独立举办!

六月

- 2nd CARRV 第二次CARRV workshop(Computer Architecture Research with RISC-V ) 将在6月2日和ISCA 2018共同举办。

- RISC-V Shanghai Day, 2018年6月30日

七月

十月

- RISC-V Day Tokyo (mid-October TBD)

十二月

招聘简讯

CNRV提供为行业公司提供公益性质的一句话的招聘信息发布,若有任何体系结构、IC设计、软件开发的招聘信息,欢迎联系我们!

整理编集: 宋威、黄柏玮、汪平、林容威、傅炜、巍巍、郭雄飞

欢迎关注微信公众号CNRV,接收最新最时尚的RISC-V讯息!

本作品采用知识共享署名-非商业性使用-相同方式共享 3.0 中国大陆许可协议进行许可。