CNRV

关注RISC-V和Chisel以及开源IC和EDA在中国的发展

RISC-V 雙周簡報 (2018-03-02)

要點新聞:

- RISC-V @ Embedded World

- GreenWaves的GAP8引發關注

RV新聞

Embedded World上的RISC-V

今年在德國舉辦的Embedded World上RISC-V大放異彩。

多個RISC-V的夥伴參展並且發表演講,當中還包含一個獨立的RISC-V Session。

更多信息見基金會網站頁面: RISC-V At Embedded World 2018

GreenWaves發布GAP8晶片和GAPUINO開發板

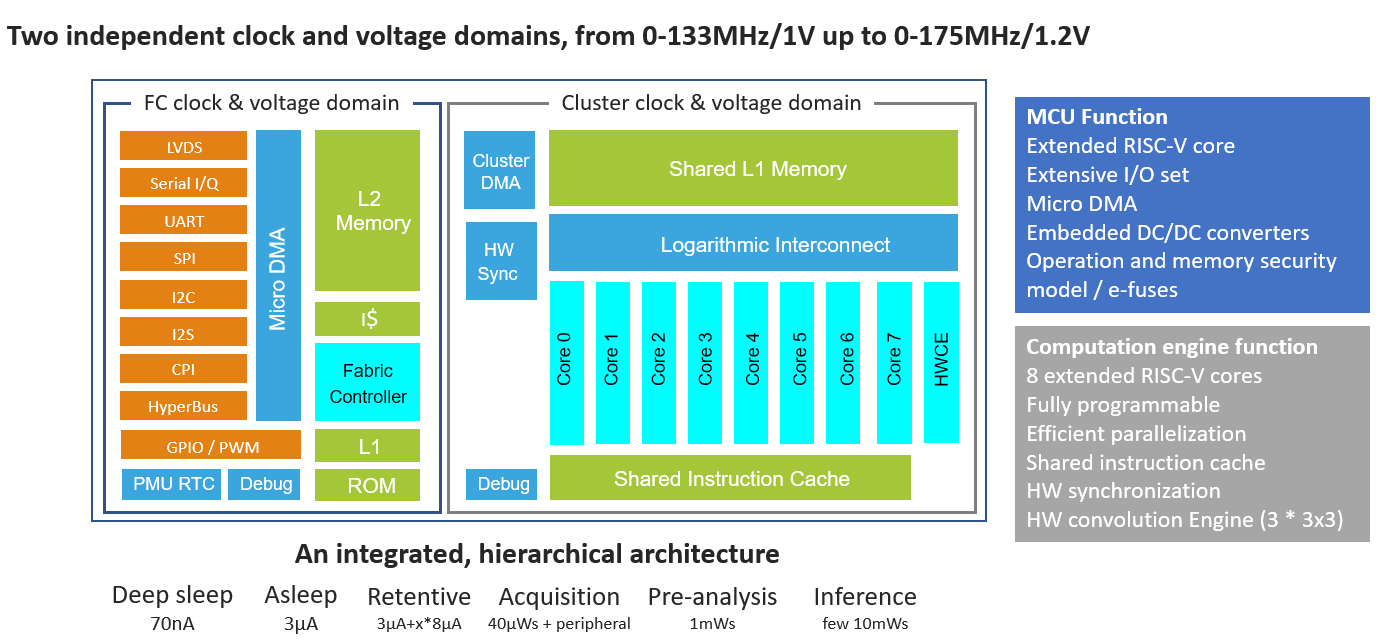

GreenWaves Technologies是一家法國的Fabless IC startup,致力於開發基於RISC-V的IoT應用處理器,使其能夠應用於由電池驅動的嵌入式設備,並在低功耗、低速率和特定計算能力場景下可靠工作長達數年。

公司的第一款產品 GAP8為終端設備提供了一種超低功耗計算解決方案,能夠對多種內容豐富的信息源(如圖像,聲音和動作)進行處理,內置的多核處理單元和神經網絡加速器讓GAP8在物聯網應用場景內遊刃有余。在能效方面,在執行某些任務時能夠做到15-20倍優於市場現有微處理器。

參考文章:GAP8 performance versus ARM M7 on Embedded CNNs

GreenWaves Technologies最近發布了售價199歐元的基於GAP8晶片的開發板 - GAPUINO。包含一個GAPUINO開發板,一個低功耗QVGA攝像頭module 以及一個多種傳感器集成板。

GAPUINO提供了一個基於GAP8並行運算處理器的開發平台,可以用於處理圖像、聲音和振動等輸入信號。開發板的參考樣例包括關鍵字識別(語音)、行人檢測或人臉檢測等。GAP8還支持較為覆雜的電源管理方案,從而實現長達數年的電池續航時間。

GAP8 SDK包含3個部分:

- RISC-V GNU工具鏈以並支持添加到GAP8中的extension指令

- 對於主控制核心目前有兩種OS支持

- PULP OS:做為PULPentry目的一部分(基於事件/線程的操作系統)

- Arm Mbed OS(將Mbed OSentry目移植用於RISC-V / GAP8)

- 多核CLUSTER開發工具: GAP8 AutoTiler,其能夠自動生成執行L2或外部存儲器之間的資料移動的代碼,並且充分利用GAP8多核架構優勢。同時包含GAP8代碼生成器庫,該庫已擁有使用GAP8 AutoTiler開發的不同算法,包括CNN層,FFT,矩陣運算,FIR濾波器等等

GAP8的架構中有8個並行的RISC-V核心可以用於做並行處理(SPMD),除了八個核心之外還包含一個Hardware Convolution Engine,這些核共享I$。晶片由TSMC 55nm工藝制造,面積7x7mm2。

小編點評:

在這個靠堆硬體吸引眼球的時代,如何平衡功耗、成本和計算能力?如何在新的AI浪潮面前迅速推出產品?如何在提供硬體的同時也提供高層次工具?如何利用RISC-V架構來提高產品競爭力?我想GreenWave交出了一份不錯的答卷。

GAP8相關報導和評論

GreenWaves Technologies Unveils GAP8

“GAP8 differs radically from the flurry of other AI focused processors, which target either far more complex applications that can’t be battery powered, or much narrower application spaces. Instead, GAP8 is precisely positioned at the crossroads of the AI, IoT and MCU worlds. The autonomous operation enabled by GAP8 dramatically reduces the deployment and operating costs of image, sound and vibration sensing devices, enabling an unprecedented scale of adoption,” said Loïc Liétar, co-founder and CEO of GreenWaves Technologies. “Furthermore, building on the RISC-V and PULP open source projects has allowed us to bring to market radical innovation with an outstanding capital efficiency at a speed that allows us to promptly serve customer demand.”

…

GAP8’s ultra-low power operation enables use cases such as

- Always-on face detection with a few mWs of power

- Indoor people counting / presence detection with years of autonomy

- Sub $15 machine vision and voice control solutions for consumer robotics

- Single chip processing for 4 microphone voice capture and 10-word speaker independent keyword spotting

They include an extended RISC-V instruction set architecture to pack more operations into each cycle, an energy optimal sign-off frequency, hardware synchronization, eight-core parallelization, a fast turn-on/switch off function achieved by putting the power management unit inside the chip, a shared instruction cache and a hardware convolution engine.

More specifically, hardware synchronization is important because, for fine-grain loops, synchronization dispatched to the eight cores could burn up to 50 percent of the sequential computing. This would drastically limit efficiency in parallelization, said Liétar. “Doing this synchronization in HW removes this limitation,” he said.

IoT apps processor boasts eight RISC-V cores

The part features eight RISC-V cores combined with a convolution hardware accelerator. It also has a separate core with an independent frequency and voltage domain. Croome said: “One side of the chip looks like an MCU; the other side is the RISC-V cluster, which shares instruction caches.”

Interestingly, Greenwaves has developed the part on an apparent shoestring, having only raised €3.1m in August 2017. “It’s a small amount of money for a start up,” Croome noted, “but we’re using open source components. We couldn’t have used anything other than RISC-V cores because that would have needed more investment.”

GreenWaves Puts Another Spin on IoT Chips

GreenWaves is a 16-person startup with headquarters outside scenic Grenoble, France. Their first (and so far, only) product is GAP8, a microcontroller intended to bring CNN smarts to cheap, battery-powered IoT edge devices. The chip combines some familiar open-source hardware with some unfamiliar, proprietary circuitry to create something the company thinks will be smarter and more power-efficient than anything the world’s many and varied Arm licensees can conjure up.

Rather than using the ubiquitous Arm Cortex-A or -M cores, GreenWaves relies on the potentially ubiquitous RISC-V design. The benefits here are twofold: RISC-V is free (as in free beer), and RISC-V permits user-defined extensions. GreenWaves took advantage of both characteristics to build itself a complex multicore MCU that’s tweaked for image, audio, and sensor processing. The idea is to make the edge-node processor smart enough that it doesn’t have to upload raw data to a smarter device upstream. Do your data-capture, analysis, filtering, and massaging right at the point of collection and you’ll save yourself time, money, and power.

感謝陳傑和張垚提供信息

Debug spec 進入45天的 public review

經過一年左右,debug spec最近進入了45天的 public review期間,按照基金會的規則,45天完後就會做ratification,標準就會確定下來。對debug spec 有興趣的朋友可以針對debug spec給予反饋。這是RISC-V 標準中,第一個進入public review的部分。隨著越來越多多核risc-v cpu 出現,小編也期待memory model 的部分能早日進入45天的public review。

- 更多細節請參考:RISC-V Debug Spec Public Review

開源硬體更新

OPENPULP - 另一個多核RISC-V 平台

PULP 團隊最近開源了他們的多核平台OPENPULP,也就是先前tape out的 Mr.Wolf。OPENPULP以架構上來說,是由一個小核控制八個大核以及加速器來運算。更重要的是,這是除了rocket以外,另一個多核的RISC-V平台。PULP團隊列出了OPENPULP的幾個特點像是:

- 2D DMA

- 支援OpenMP programming model

- shared instruction cache

- 針對硬體加速器的支援

-

支援 atomic accesses on a multi-banked scratchpad memory 的 新版互連

- 更多細節請參考PULP官網 以及 PULP 在 HPCA 的slides

開源軟體更新

risc-v gdb patch v2

在工具鏈(gcc,llvm,gdb,glibc,binutils,newlib)中,risc-v的 gdb port一直是個缺乏關註的環節,embecosm 的 Andrew Burgess 最近開始針對gdb 提交patch。期待 gdb 也能早日合併主線。

QEMU patch v7

來自 SiFive 的 Michael Clark 持續的在提交 QEMU patch,並在最近針對合併主線,做了一次port submission。

- 更多細節可以參考 Michael 所貼的status update:QEMU status update

Fedora/RISC-V: Runnable stage 4 disk images

Richard 持續的推進fedora bootstrap的情況下,目前的 fedora 有 bootable disk images了。按照Richard整理的結果,目前這個port包含:

- OpenSSH server

- dnf repository offering about 6000 packages

- most Fedora @Core packages

- Perl 5.26

- Python 2.7 & Python 3.6

- GCC 7.3.1

- systemmd

如果想要嘗試一個簡單的linux distribution,可以使用這個 port。除了Fedora以外,debian這端,也有非常多的bug report,看來兩個linux distribution 在risc-v 這塊都有不少進展。

技術討論

由支持運行時關閉RVC支持而引發的一系列問題

RVC,即RISC-V的壓縮指令集,是一個非常有用的RISC-V指令級extension。 在支持RVC的處理器上,有可能需要臨時關閉RVC支持。 其具體操作就是清除misa.Cbit。 在清除misa.Cbit後,處理器應該嚴格執行32bit指令並要求指令對齊32bit address 。

最先由形式化workgroup提出,關閉RVC操作會引發未定義的行為。 這種未定義的行為簡單來說有兩個:

- 如果清除misa.Cbit的CSRW指令不在32bit對齊的 address 上,緊接著的下一條指令有可能發生 address 不對齊的錯誤。

- 如果清除misa.Cbit的CSRW指令發生在異常響應程序中,而此時mepc中保存著一個 unaligned 的異常返回 address ,那麽過一會兒mret時也會發生未對齊錯誤。

這裏大家在激烈爭論的問題是,如果出現這種情況,到底算哪一條指令出現了異常。比如對第一個問題,到底是算CSRW指令錯誤,還是後續的指令 unaligned 錯誤?

根據現在的修改預案,解決方案大致如下:

- 如果清除misa.Cbit的CSRW指令沒有對齊,CSRW指令會清除misa.Cbit。但是後面的指令會報出 address 不對齊異常。mepc會記錄 unaligned 的指令 address 。

- 如果misa.C被清除後,mret跳回直一個 unaligned address ,mret指令正常完成,並且系統優先級返回異常發生時的優先級,然後報mepc所指向的指令 address unaligned 錯誤。

- 如果jmp和branch試圖在misa.C為低的時候將pc置為 unaligned address ,立即報jmp和branch指令錯誤。

這裏就有些不對稱的問題了。mret也是跳轉,卻總是正確完成,報後面指令的 address 錯誤。而jmp/branch卻會報當前指令的錯誤。 這裏的問題是,如果mret指令會引發異常,將會破壞硬體的異常處理,有可能導致不能在異常處理後正確返回異常之前的優先級。 jmp和branch指令立即發生異常,則是為了能更好的調試。 如果jmp和branch將pc設為 unaligned address ,而報後面指令錯誤。發生錯誤時很難發現錯誤的原因是跳轉錯了 address 。

RDCYCLE的意義

鑒於最近Krste在ISA標準中解釋了hart的定義,Liviu Ionescu提出了新問題: “那麽,RDCYCLE讀取到的是一個處理器(processor core)執行的時鐘周期數是不是不準確了呢?” 結果,為了解釋這個,Krste準備又要在標準裏加一大段解釋了。 解釋太長,具體看這裏:https://github.com/riscv/riscv-isa-manual/issues/140#issuecomment-368856451

簡單說呢,其實是這樣的: 首先,RDCYCLE讀到的是一個處理器core執行的時鐘周期數而不是一個hart的周期數。 原因是因為一般的SMT處理器並不能嚴格獲得一個hart所執行的周期數。 但這並不是一個問題。RDCYCLE本來就只是一個單調隨時間正向增長的計數器。 這裏的確是一個不準確的定義,但是這個定義的確也很難準確。 不準確的定義不代表就不能被定義。

進一步的 cache prefetch 計劃

Max Hayden Chiz在hw-dev列表中進一步介紹了關於為Rocket-Chip(Rocket和BOOM)添加 hardware cache prefetch 的計劃, 並號召有時間的人一起來完成。 具體的計劃可見郵件列表。

進一步的討論中又冒出了很多好點子。比如說Jacob提出我們可以找到32個 register 中使用較多的幾個 register ,然後用硬體預測 register 的步長。如果發現 register 有固定步長變化,同時被用於 access 內存,則可用於指導自動 cache prefetch (stride prefetch)。同時,為了防止 prefetch 被用於 cache 側信道攻擊, prefetch 的 cache 塊應該放入單獨的 cache 空間,只有當 cache 塊真的被 access 才進入一級 cache 。

代碼更新

即將到來新的一輪Rocket-Chip變量名變更

一個設計的成熟度有時候其實依賴於很簡單的東西,比如頻繁使用的變量名在前後版本中保持一致。 不過,Rocket-Chip的設計者們決定,他們又要更名了。 這回:

- coreplex要更名為subsystem

- HasPeripheryBus的定義被BaseSubsystem涵蓋

- Clint變大寫為CLINT

- 各個bus被重名為:ibus, sbus, pbus 和 fbus

希望這回更名能持續的久一點。

- 具體的更名代碼在Rocket-Chip的PR #1190

實用資料

All Aboard, Part 10: How to Contribute to the RISC-V Software Ecosystem

Palmer在這篇 blog 中整理了 RISC-V software eco 目前的狀況。有興趣採用risc-v的同學可以參考。

市場相關

IAR Systems加入RISC-V基金會

國內朋友比較熟悉的嵌入式IDE廠商IAR最近加入了基金會,讓我們期待IAR未來在RISC-V的支持。

“The RISC-V technology and ecosystem are currently evolving rapidly and there are a lot of exciting innovation going on connected to the RISC-V community,” comments Anders Holmberg, Director of Corporate Development, IAR Systems. “We have customers currently looking at working with RISC-V in upcoming design projects, and they have expressed a need for high-performance commercial tools with professional technical support. By adding our leading tools to the ecosystem, we respond to our customers’ needs, and also create new business potential within the RISC-V community.”

Link: IAR Systems commits to bring leading development tools to the growing number of RISC-V users

Imperas發布用於快速評估Linux的RISC-V RV64GC High-Performance Extendable Platform Kit

Imperas發布了可以用來讓開發人員評估RISC-V Linux系統的平台開發包。

Imperas virtual platform products provide for a broad range of software verification and profiling capabilities. Model code coverage and instruction coverage enable an effective measure of software verification quality to be established. A broad range of profiling tools, including timing performance and power consumption, allow for effective quality metrics to be established, prior to hardware availability. An advanced debug solution is also included with advanced features designed specifically for complex multi-core software.

Link:

CEVA加入RISC-V基金會並且聲稱在其解決方案中使用RISC-V處理器

CEVA 最近加入了RISC-V 基金會,並在這篇新聞中介紹他們在CEVA 的 Wifi IP 中使用risc-v core 的經驗。

CEVA’s experience with RISC-V

Like these companies, CEVA has been intrigued by the potential of RISC-V, especially in regards to our RivieraWaves Wi-Fi and Bluetooth IPs (Figure 1). These communication technologies require a small processor to execute the protocol stacks and our aim was to create an integration-ready reference platform that offers our customers freedom in the choice of processor. In terms of requirements, the horse-power needs are modest, even for advanced Wi-Fi configurations, since the IPs have been architected for very low power operation. The brief calls for a low gate count, power efficient, mature processor, with a familiar, commercial-grade software development environment that can produce die-saving compact code. The design must be suitable for easy deployment (at full speed) in FPGA and in ASIC/ASSP and it must have a legal framework compatible with our business of licensing IP.

…

The RISC-V processor implementation is perfectly matched to typical IoT device requirements in terms of performance and die cost, with a Coremark/MHz figure of 2.44 in a gate count of under 20Kgates. Blending perfectly with the low power architecture of the RivieraWaves IP, the RISC-V based Bluetooth platforms offer the industry’s lowest clock frequency and most power efficient Bluetooth low energy and Bluetooth dual mode solutions. For heavier data loads, the RivieraWaves Wi-Fi RISC-V platforms are the world’s smallest fully-integrated solutions, and scale from basic 1x1-11b-1Mbps up to 2x2-11ac/ax MU-MIMO-1201Mbps. These pre-integrated RISC-V based platforms significantly reduce the development time and bill-of-materials for CEVA’s customers, allowing for rapid product development and market introduction.

Link:

- Open source RISC-V architecture is changing the game for IoT processors

- CEVA Extends its IP Platforms for Bluetooth and Wi-Fi with RISC-V

Express Logic的基於RISC-V的工業級X-Wave IoT平台

Express Logic發布了其工業級X-Wave IoT平台,平台基於ThreadX RTOS平台並提供Microsemi Mi-V RISC-V處理器的完整的支持。

ThreadX RTOS通過了多個Security認證,小編認為這是其主要的優勢。

In addition to the performance and size advantages of the X-Ware IoT Platform, Express Logic’s ThreadX, FileX, and NetX Duo have attained the highest level of safety certifications. They include IEC 61508 SIL 4, IEC 62304 Class C, ISO 26262 ASIL D, EN 50128 SW-SIL 4, UL 60730-1 Annex H, CSA E60730-1 Annex H, IEC 60730-1 Annex H, IEC 60335-1 Annex R, and IEC 60335-1 Annex R, 1998.

Link: Express Logic’s X-Ware IoT Platform® Brings Industrial-Grade IoT Support to RISC-V Architecture

會議征稿

第八屆 RISC-V Workshop Call for Papers

在西班牙舉辦的第八屆RISC-V workshop開始徵稿了! 有興趣的同學可以趕快把握機會!

暴走事件

二月

-

FOSDEM’18 2018年2月3-4日,FOSDEM (Free and Open Source Developers’ European Meeting)將在比利時的布魯塞爾舉行。

-

PULP WORKSHOP AT HPCA2018 2018年2月25日,在維也納的HPCA中,會有一場跟Pulp 有關的workshop。PULP小組會介紹PULP最新的發展,和他們未來的走向,包括 PULP-CAPI (Coherent Accelerator Processor Interface) 和 Ariane (Next generation of 64-bit RISC-V implementations)等。詳情可參考 pulpino mailing list 中的 < PULP newsletter - 4Q2017 >。

-

Embedded World 2018 2018年2月27日,在德國 Nuremberg 的 Embedded world會有一整天跟RISC-V有關的演講。包括 Microsemi, Mentor Graphics等公司都會給演講。AMD的CTO Mark Papermaster 也會給一個 Conference Keynote。

三月

- OpenEmbedded/Yocto on RISC-V 2018年3月12-14日,在ELC NA (Embedded Linux Conference North America 2018),來自Comcast的 Khem Raj 會給一場關於 OpenEmbedded/Yocto on RISC-V的演講。

五月

- 8th RISC-V workshop 第八次RISC-V workshop將在5月7-10日在西班牙舉辦。

六月

-

CNRV的成員和愛好者們正在RISC-V基金會的支持下籌備一場線下活動,時間暫定為2018年6月30日,目前暫定在復旦大學舉行。有任何建議、意見和想法,都可以發郵件給群頭 xfguo@xfguo.org。

-

2nd CARRV 第二次CARRV workshop(Computer Architecture Research with RISC-V ) 將在6月2日和ISCA 2018共同舉辦。

招聘簡訊

CNRV提供為行業公司提供公益性質的一句話的招聘信息發布,若有任何Architecture、IC設計、軟體開發的招聘信息,歡迎聯系我們!

整理編輯: 宋威、黃柏瑋、郭雄飛 繁體版維護者:黃柏瑋

歡迎關註微信公眾號CNRV,接收最新最時尚的RISC-V訊息!

本著作係採用創用 CC 姓名標示-非商業性-相同方式分享 3.0 台灣 授權條款授權.