CNRV

关注RISC-V和Chisel以及开源IC和EDA在中国的发展

RISC-V 雙周簡報 (2018-02-15)

要點新聞:

- SiFive發布可運行Linux的HiFive Unleashed開發板

- PULP開源64-bit處理器Ariane

寫在前面

2018農歷新年還沒過,我們就看到兩個好消息,SiFive和PULP都有和可運行Linux的CPU的好消息,如果說去年RISC-V在MCU上遍地開花,那麽今年這個RISC-V Linux元年也一定會很精彩。新的平台和新的板子總能夠讓軟體開發人員為之興奮,小編已經迫不及待躍躍欲試。下半年我預計就會看到大量的操作系統移植,開源顯卡是不是也離我們不遠了哈哈。

CNRV祝大家狗年旺旺旺!

RV新聞

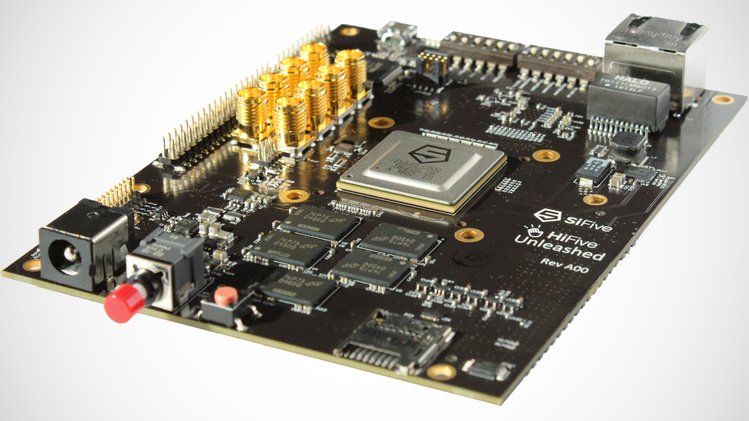

SiFive的HiFive Unleashed開發板和Freedom U540 SoC晶片

SiFive最近發布了其HiFive Unleashed開發板,並在Crowdsupply上開始同步預售,最早一批75塊開發板將於3月30日發貨。

在這塊開發板上搭載的是SiFive最新的Freedom U540 SoC晶片,小編估計其早期版本搭載的是MPW工程樣片,後面則開始發售搭載量產版本的晶片。

關於Freedom U540 SoC,SiFive官方發布的Spec如下:

- (目前)最快的RISC-V處理器

- (目前)唯一的可以運行Linux的RISC-V SoC晶片

- 多核(4大核+1小核)處理器並且支持緩存一致性,主頻高達1.5GHz

- 4個U54 RV64GC應用處理器,並支持Sv39虛擬內存

- 1個E51 RV64IMAC用於管理的CPU

- 2MB一致性二級緩存

- 64-bit DDR4控制器並支持ECC

- 一個千兆以太網MAC

- 用TSMC 28nm工藝制造

這塊開發板目前還支持通過FMC接口來連接FPGA開發板等外部接口卡,小編猜測是可以通過ChipLink來直接和片外的FPGA進行高速通信。

與此同時,在FOSDEM’18上,來自SiFive的Palmer和Yunsup還發表演講向大家公開了更多的相關細節。現場還通過在搭載在FPGA上的顯示module 和接口向觀眾演示了FPS遊戲Quake比如,SiFive還將開源他們的L2$設計,之前的rocket-chip中L2 Cache的設計被發現存在問題,所以社區也一直等待在這方面能夠有所進展。

Links:

以下是業界對HiFive Unleashed的一些相關評論:

DataCenterKnowledge網站在看到RISC-V和HiFive的演講後發表了《Is Open Source RISC-V Ready to Take on Intel, AMD, and ARM in the Data Center?》的文章,其在文章中表示:

While software is eating the world, open source hardware might soon be eating the data center. Definitely not tomorrow or next month, and probably not even next year, but sooner than you think, there might be as much open source hardware as the old-fashioned proprietary kind running data centers.

Need proof? Take a look at RISC-V, an open processor architecture.

Link: Is Open Source RISC-V Ready to Take on Intel, AMD, and ARM in the Data Center?

LinuxGizmos網站則發表了文章《RISC-V gains momentum as it moves from MCUs to Linux-friendly SoCs》,當中提到封閉的ARM和Intel x86限制了創新、減緩了上市時間並且增加了成本。

RISC-V’s timing seems to be right, as the growing acceptance of open source software and hardware logically leads to a desire to open up of the processor. Opaque chip designs often create obstacles and blind spots — not only for open source projects, but also semiconductor vendors. Conceivably, hidden issues such as Intel’s Spectre and Meltdown security problems might have come to light more quickly in the open source spotlight.

There’s also a sense that the dominance of two closed source architectures — ARM and Intel x86 — is limiting innovation, slowing time to market, and increasing cost. In addition, RISC-V advocates claim that both ARM and x86 platforms are burdened by legacy code. By comparison, RISC-V is starting with a clean slate of modern components.

Link: RISC-V gains momentum as it moves from MCUs to Linux-friendly SoCs

DesignNews發表了《First Open-Source RISC-V SoC for Linux Released》,當中提到:

But how does SiFive expect an open-source board to stand out in an ever-crowding market? And why should a company, particularly in a space like IoT, choose open source over any of the other solutions available? “ I certainly believe IoT will be solved by having lots of customization,” Kang said. “I believe IoT inherently is not a one-size-fits-all type of market. What that means is you’re not going to be able to have one killer chip that does everything. What you’re going to need is to be able to customize or get your partners to customize the silicon to meet the specific problems that will come up. And I will argue that RISC-V is great for customization.”

Link: First Open-Source RISC-V SoC for Linux Released

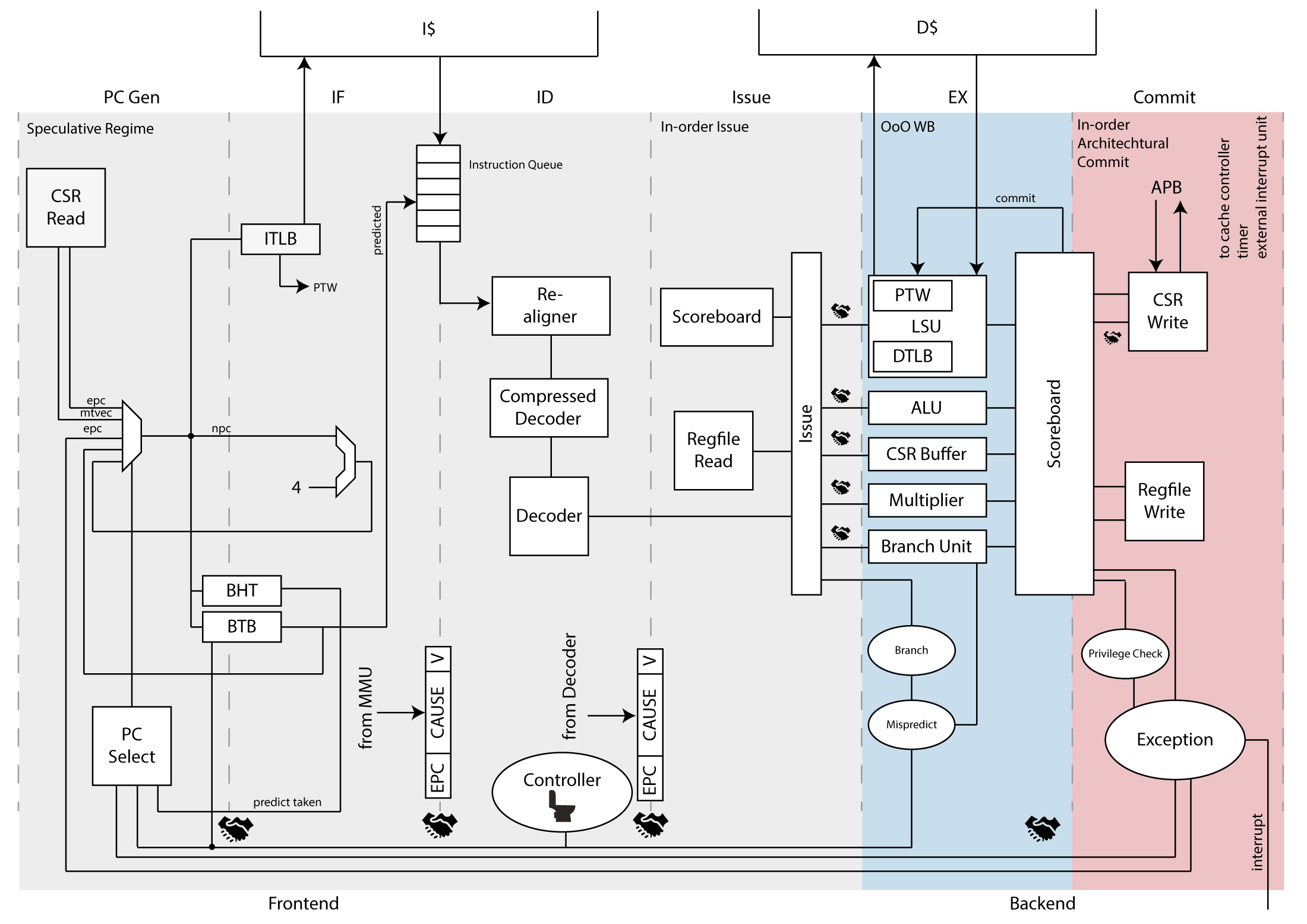

PULP家族新增64-bit處理器Ariane

PULP的研發團隊最近設計了一款6級流水線的可以運行Linux或者Unix操作系統的RISC-V處理器。

相關Spec如下:

- 6-stage, single issue, in-order

- RV64IMC,User-Level ISA v2.1

- Privilege v1.10,實現了M、S、U三種模式

- 面積可配置、分離的TLB、硬體PTW和 branch predictor

Github Repo

PULPissimo

PULP團隊在最近發布了一個新的單核SoC平台PULPissimo。

PULPissimo是一個類似PULPino的平台。相比與PULPino,PULPissimo是在完整性和覆雜性上有明顯的進步,事實上PULPissimo系統是最近所有多核PULP晶片的主要SoC控制器。

PULPissimo架構包含:

- RI5CY或者zero-riscy作為主要處理器

- 自管理的I/O子系統(通過uDMA來進行自主操作,無需CPU幹預)

- 新的存儲子系統

- 硬體處理引擎的支持(Hardware Processing Engines)

- 新的簡易中斷控制器

- 新的外設

- 新的SDK

此外,其I/O接口中小編還看到了Camera Interface (CPI)。簡單評價一下的話,小編認為這個平台的目標是為了IoT應用而量身打造的,自管理的I/O子系統能夠很好的解決低功耗的問題,而豐富的接口則能夠支持圖像採集等應用。

Link:

- PULPissimo Github Repo

- PULP team 的 郵件列表

PULP代號Mr. Wolf流片成功

前面提到了PULPissimo,最近有新聞就表示PULP基於TSMC 40LP工藝的群核(cluster based processor)晶片,內含8個RIC5Y處理器和1個zero-riscy處理器。8個大核支持RV32IMCF以及PULP自有的DSP指令extension。

此外PULP團隊也提到

“We actually plan to release the entire Mr. Wolf code later this year. Of course, various NDAs prohibit us from releasing technology specific data, our releases contain only System Verilog code, testbenches and associated files for verification,” Gurkaynak.

Link: RISC-V processor Mr Wolf arrives to solve problems

開源軟體更新

OpenJDK RISC-V port ?

在 glibc和linux合併主線以後,許多人開始關註軟體上的下一步,像是OpenEmbedded/Yocto, Debian, 和Java/OpenJDK。像是Palmer 最近就在sw-dev開始討論如何開始移植OpenJDK的問題。

有興趣參與或討論的請參考郵件列表: Project proposal: RISC-V port

技術討論

到底什麽是一個 hart?

去年11月底,郵件列表上針對 hart 的精確定義以及 core 和 hart 之間的區別有一個熱烈的討論。由於在許多RISC-V 文檔中,core 和 hart 常常被交互使用,Liviu Ionescu 提議在 ISA manual 中加上 hart 的精確定義。 Prof Krste 最近提交了這個更新。其中,core 和 hart 分別定義如下:

Core:

A component is termed a core if it contains an independent instruction fetch unit. A RISC-V-compatible core might support multiple RISC-V-compatible hardware threads, or harts, through multithreading.

Hart:(部分擷取)

From the perspective of software running in a given execution environment, a hart is a resource that independently fetches and executes RISC-V instructions within that execution environment. In this respect, a hart behaves like a hardware thread resource even if time-multiplexed onto real hardware by the execution environment.

從定義中,hart 代表的是在環境中讓程式執行的資源,至於底層是Emulation、硬體、還是用M:N的方式 multiplexed,對於程式來說,都是沒有影響的。Core 則是指有 IFU 的 component。目前看來,hart的定義是清晰了許多。

- 郵件列表上的討論:Definition of “hart” on sw-dev

- github上的討論和commit : Added clearer definitions of execution environments and harts. , 原始的issue

- Krste 所引用關於hart的原始論文 :

- [1] Pan, Heidi, Benjamin Hindman, and Krste Asanović. “Composing parallel software efficiently with lithe.” ACM Sigplan Notices 45.6 (2010): 376-387.

- [2] Pan, Heidi, Benjamin Hindman, and Krste Asanovic. “Lithe: Enabling efficient composition of parallel libraries.” Proc. of HotPar 9 (2009).

已被支持的硬體性能監視功能

也許大家都和小編一樣沒有註意到現有的Rocket-Chip已經支持較為覆雜的性能計數器了。 在最近關於Rocket-Chip的一個問答中,透露出現有Rocket-Chip,或者更準確的說基於Rocket-Chip的SiFiveextension已經集成了較為覆雜的功能計數功能。 這個功能由mhpmevent CSR控制,其計數器的值則有mhpmcounter CSR提供。 mhpmevent的低8位可以取三種取值:0,指令事件;1,微結構事件;2,內存系統事件。同一時刻,性能計數器只能記一種類型的事件。 在每種類型中,mhpmevent的高56位是一個選取細節事件的bitmap,如果任何一個bitmap使能的事件發生,則會導致mhpmcounter自增。

Link: 詳細的性能記數配置

代碼更新

用戶和 kernel page table 分離方案被提交到riscv-isa-manual並預進入priv spec v1.11

一月下旬,Jacob Bachmeyer將上個月在rv-dev郵件列表中討論的用戶和 kernel page table 分離方案提交到了RISC-V ISA的Git Repo。 根據他和Andrew的對話,該方案很有希望作為一個指令集extension被寫入Priveleged Spec v1.11版,即即將公布的下一版本。 具體的方案現在都可以在PR看到:https://github.com/riscv/riscv-isa-manual/pull/128

簡單說,這個方案提出了一個名為Sdas (Standard Extension for Disjoint User/Supervisor)的extension。 該extension增加了一個名為suatp的新CSR。該CSR指向用戶空間的 page table base address 。 如果該extension不被支持,即仍然使用以往用戶和 kernel 共享空間的 page table 方式,suapt和satp的值嚴格相等,都指向共享 page table 的 base address 。 如果使用該extension,satp指向 kernel page table 的 base address ,suapt指向用戶 page table 的 base address 。 kernel page table 和用戶 page table 使用不同的ASID防止TLB刷新。

同時為了支持兼容性,無論是否支持extension,當 kernel 寫satp時,suatp的值都會對應改變,保證在兼容情況下不需要處理suatp。 在支持extension的時候,由於 kernel 空間一般被多個 process 共享,所以上下文切換並不需要修改SATP,而只需要更改用戶 page table ,即修改suatp。

具體細節請參見PR

QEMU port v4 and v5

Michael Clark 最近提交了QEMU port 的第四版和第五版。在這兩版中,他修改了不少Richard Henderson所發現的bug,同時做了些code cleanup。由於Michael目前在Sifive工作,這些QEMU patch中,還包含了SiFive Freedom U500 RISC-V Machine等實現的 Emulation。期待QEMU能早日合併主線。

Link: RISC-V port v4 & v5

Linux kernel : RISC-V changes for 4.16

最近的更新中包含了一些重要的基礎建設更新。像是:

- 來自 Andes 的 Alan Kao 加上了 ftrace support

- 加上 ZONE_DMA32: 不同於ZONE_DMA只支援16MB,ZONE_DMA32可支援32bit的DMA。

- TLB shootdown 現在只有需要被shootdown的才會動作,而不再是針對所有hart。

以小編對 kernel 微薄的理解,ZONE_DMA32 和 ftrace都是 kernel 非常基礎的功能。可見RISC-V port 還有許多路要走,但另一個角度講,對於有興趣送 patch的同學,也是個大好機會,可以多多把握。

- 更多詳情請參考:RISC-V changes for 4.16

CNRV網站更新

會議徵稿

CARRV 第二屆 @ ISCA 2018

CARRV workshop (Computer Architecture Research with RISC-V) 開始徵稿了。這次是在六月的ISCA 2018舉辦。有興趣的同學可以把握機會!

- Link:CARRV

暴走事件

二月

-

FOSDEM’18 2018年2月3-4日,FOSDEM (Free and Open Source Developers’ European Meeting)將在比利時的布魯塞爾舉行。

-

PULP WORKSHOP AT HPCA2018 2018年2月25日,在維也納的HPCA中,會有一場跟Pulp 有關的workshop。PULP小組會介紹PULP最新的發展,和他們未來的走向,包括 PULP-CAPI (Coherent Accelerator Processor Interface) 和 Ariane (Next generation of 64-bit RISC-V implementations)等。詳情可參考 pulpino mailing list 中的 < PULP newsletter - 4Q2017 >。

-

Embedded World 2018 2018年2月27日,在德國 Nuremberg 的 Embedded world會有一整天跟RISC-V有關的演講。包括 Microsemi, Mentor Graphics等公司都會給演講。AMD的CTO Mark Papermaster 也會給一個 Conference Keynote。

三月

- OpenEmbedded/Yocto on RISC-V 2018年3月12-14日,在ELC NA (Embedded Linux Conference North America 2018),來自Comcast的 Khem Raj 會給一場關於 OpenEmbedded/Yocto on RISC-V的演講。

五月

- 8th RISC-V workshop 第八次RISC-V workshop將在5月7-10日在西班牙舉辦。

六月

-

CNRV的成員和愛好者們正在RISC-V基金會的支持下籌備一場線下活動,時間暫定為2018年6月30日,目前暫定在覆旦大學舉行。有任何建議、意見和想法,都可以發郵件給群頭 xfguo@xfguo.org。

-

2nd CARRV 第二次CARRV workshop(Computer Architecture Research with RISC-V ) 將在6月2日和ISCA 2018共同舉辦。

招聘簡訊

- 華為海思自研DSP團隊招聘:華為海思DSP團隊招聘DSP設計、驗證、工具鏈等相關職位,同時也招聘SoC的設計、驗證工程師以及ESL工程師。簡歷請發至:yingjuanjuan@huawei.com

- 華為海思手機晶片團隊招聘:招聘數字晶片設計、驗證和FPGA開發等職位,簡歷請發至fangzhihua@huawei.com

CNRV提供為行業公司提供公益性質的一句話的招聘信息發布,若有任何Architecture、IC設計、軟體開發的招聘信息,歡迎聯系我們!

整理編集: 宋威、黃柏瑋、郭雄飛 繁體 translation 維護者:黃柏瑋

歡迎關註微信公眾號CNRV,接收最新最時尚的RISC-V訊息!

本著作係採用創用 CC 姓名標示-非商業性-相同方式分享 3.0 台灣 授權條款授權.