CNRV

关注RISC-V和Chisel以及开源IC和EDA在中国的发展

RISC-V 双周简报 (2017-10-26)

要点新闻:

- 武汉聚芯和北京九天开源了其蜂鸟E200系列处理器

- CARRV论文发布

- RISC-V 工具链资料搜集

- Spike Internal 文档

- 7th RISC-V workshop workshop议程发布

- RISC-V toolchain中的Linker Relaxation(Palmer的 All aboard Part3)

- 使用编译参数在汇编代码中选择性地使用RVC压缩指令

- 破坏执行中函数调用和函数返回严格配对的主要原因

- IQ-Analog的14nm芯片使用了RISC-V 的 CPU

RV新闻

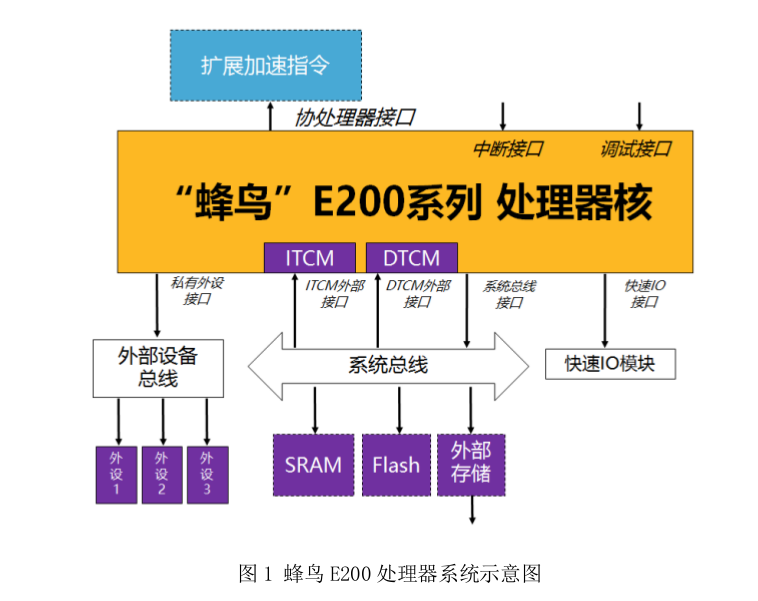

武汉聚芯和北京九天开源了其蜂鸟E200系列处理器

武汉聚芯和北京九天最近在GitHub上开源了其蜂鸟E200系列处理器,这是国内由商业公司开源的第一款支持RISC-V指令集的处理器。

蜂鸟处理器采用2级流水线结构,在其发布的文档中可以看到其功耗与面积均优于同级ARM Cortex-M0+核。处理器核实现了RV32I/E/A/M/C/F/D等指令子集的配置组合,但目前只支持Machine Mode。在License上也采用了非常宽松和商业友好的Apache License。蜂鸟E200主要面向极低功耗与极小面积的场景而设计,非常适合于替代传统的8051内核或者Cortex-M系列内核应用于IoT或其他低功耗场景。

处理器的作者,也是CNRV群的活跃成员胡振波表示,开源是这款这次发布的重点,并希望让国内的IoT用户免费使用,而且打出了”成为国内的下一个8051“的口号。作者同时也号召有兴趣参与这个项目的同学一起加入,具体的联系方式见下面的GitHub 页面。

下图是蜂鸟E200的系统示意图(摘自其文档)

- GitHub Repo:https://github.com/SI-RISCV/e200_opensource

7th RISC-V workshop议程发布

7th workshop的议程发布了。内容包括 RISC-V 架构、软件、硬件、模拟环境、应用等各个方向。GF, Lauterbach, Express Logic (ThreadX RTOS)及许多公司都会带来演讲。

IQ-Analog的14nm芯片使用了RISC-V CPU

IQ-Analog的Ken在先前宣布了他们公司的 14nm 芯片,同时采用了ETH-Zurich及picorv32的RISC-V核。最近,测试芯片生产完成并在200MHz下部分的测试成功。Ken在讨论区中介绍了他们的配置,并感谢社群对RISC-V的支持和维护。

At IQ-Analog, we received our first ever GF 14nm ASIC test chip a couple of weeks ago and assembled evaluation boards >containing the chip this past Thursday. After a bit of a slow startup, we were able to download and execute code yesterday >via JTAG to both the NanoRisc5 (in-house grown picorv32 variant with debug spec 0.9 debugging added) and the ETH-Zurich >versions of the RISC-V cores! While we have not bought up the 1GHz clock source yet to test full speed operation (1 GHz for NanoRisc5, 500 Mhz for ETH- >Zurich), we have been able to conduct these initial tests using a slower 200 MHz “debug clock input” path. We still have a >lot of things to bring up and test on this ASIC, but I wanted to share the news of working RISC-V cores in 14nm and extend a >thank you to everyone in the RISC-V community for developing the RISC-V architecture and intrastucture.

OSDT中关於 RISC-V 和 coreboot 的演讲

在刚刚结束的OSDT2017开源开发工具大会中,有一场跟RISC-V有关的演讲:《固件自由之路——RISC-V架构下的coreboot》。来自HardenedLinux的王翔给大家介绍了RISC-V / coreboot以及移植coreboot到HiFive1的经验。

coreboot为一个开源的固件框架,用于进行最初的硬件初始化。可以加载执行linux镜像、elf文件。可以加载执行各种程序:

- SeaBIOS : 开源BIOS实现

- TIanoCore : 开源UEFI实现

- GRUB : 一个通用开源的引导器

- Etherboot : 一个通过网络启动操作系统的引导器

演讲幻灯片:https://git.io/vFftv

Microsemi 发布 Mi-V 嵌入式整合方案

Microsemi最近发布了针对RISC-V 生态圈 的 Mi-V整合方案,将开发工具、开发板、操作系统、RISC-V 软核等一起整合起来。操作系统方面合作的厂商包括 Huawei LiteOS, Micrium µC/OS-III 和 ThreadX,同时也支援FreeRTOS。Microsemi 希望藉由这样的整合加速RISC-V生态圈的发展。

- 新闻连结:http://t.cn/RWoT1Yl

技术讨论

使用编译参数在汇编代码中选择性地使用RVC压缩指令

在全局禁止使用RVC指令的时候,汇编代码可以通过在代码中局部地启用RVC编译参数来启用压缩指令。 在如下的例子中:

.option push;

.option rvc;

c.addi a0, 1;

c.slli a0, 1;

.option pop

在.option rvc;和.option pop之间便可以使用RVC指令。而之外的部分,则会只能使用正常指令集。

- Andrew Waterman举的例子:https://goo.gl/iMoTy1

破坏执行中函数调用和函数返回严格配对的主要原因

在使用控制流一致性(CFI)保护系统安全的方法中,利用硬件或软件的影子栈来跟踪合法的函数调用是一个重要方法。 但是显式操作系统和软件的函数调用与函数返回并不是严格配对的。有的时候一个返回可能回调多个函数的压栈。 最近邮件列表中便问到了这样的问题。导致这种不一致性的主要原因是什么。Andrew的回答还是非常清楚的。 对于RISC-V来说,主要原因是长跳转(longjmp/setcontext)

Tail calls don’t generally lead to unmached call-return pairs; the tail-callee’s return will match the original call.

The main thing that screws up the return-address stack is context switching (in the kernel, or in userspace via longjmp/setcontext).

不明白这里长跳转的同学请脑补longjmp。这是迅速异常处理和可重入的一个重要概念。

- 邮件列表的讨论:https://goo.gl/sPTvvu

在反汇编中使用原始机器指令和机器寄存器

使用objdump对可执行文件进行反汇编默认使用宏指令代替特殊指令(比如用li a5, 3代替addi x15, x0, 3)和使用ABI寄存器命名代替机器命名(用a5替代x15)。如果需要反汇编成最原始的机器代码和机器寄存器,可以使用 --disassembler-options=no-aliases,numeric参数。

- 邮件列表中的讨论:https://goo.gl/As1jec

代码更新

Rocket-Chip 初步支持覆盖

Rocket-Chip 最近在Chisel代码中加入了对覆盖(cover)的支持。覆盖是硬件测试的基本概念。覆盖率用来检测仿真是否触发了各个信号的所有编码状态或控制逻辑的所有分支。不过现在的覆盖支持看起来还刚刚开始,被标注为覆盖检测的信号并不会真的计算覆盖率。也或许SiFive已经在内部测试简单的覆盖支持。

- Rocket-Chip PR #998 https://git.io/vd7D3

BOOM 支援了更好的 WFI实现

在最近开发分支的一次更新中,BOOM有了不少更新,包括实现了 sfence.vma,以及将WFI做了更好的实现。WFI (Wait for Interrupt)是个让处理器能进入低功耗状态的指令。先前的BOOM是用 NOP 来实作WFI,pipeline并没有停止。这次,WFI将会触发 csr_stall 这个信号。这个信号会被接到ROB中,使 ROB的 commit 停止,藉由这样来达到停止pipeline的效果。

- BOOM 开发分支的重要代码更新: https://git.io/vFftp

- BOOM 的issue #17:https://git.io/vFfqJ

实用资料

CARRV论文发布

CARRV (First Workshop on Computer Architecture Research with RISC-V) 的論文发佈了。这次的内容涵盖 RISC-V 的各个方向,包括模拟器(gem5)、SIMT、rv8二进制转换器、Rocket-Chip的 diplomacy pattern 等等。感觉未来用RISC-V当作平台的研究将越来越多。

- 详细的论文连结可参考:https://carrv.github.io/

TileLink相关的Paper

在CARRV上TileLink的作者们发表了一篇相关的论文,《Diplomatic Design Patterns: A TileLink Case Study》用来介绍其设计理念。以下为摘要的翻译。

随着现代的 SoC 包含越来越多复杂专一的硬件部件,通过共享总线的方式集成到统一的地址空间。由于所有互连的模块都得相互满足所需条件,需要花大量的劳动力并且容易出错。模块化 RISC-V 的瓶颈是需要集成各种处理器、总线和大量从设备,随之而来的复发度激发了开发新工具和方法学来满足设计复杂的和参数化 SoC 的需求。

Diplomacy 是一个 parameter negotiation 框架,用于参数化地实现具体的协议。除了确保系统的各个终端设备相互的兼容性之外,Diplomacy 可以让各设备基于该系统的其他设备的条件来专有化它们自己。TileLink 是参数化程度高、扩展性强(适用于各种规模的芯片)和共享主存的总线互连标准。TileLink 和 Rocket-Chip generator的实现利用了 Diplomacy 以兼容不同层次的协议来满足特殊的需求。

Diplomacy 把相互连接的拓扑结构抽象成一个有点和边构成的图。节点表示用 diplomatic 参数生成(emit)的具体硬件,边表示成对的主从设备之间的接口方向,其连接的 source 节点表示主设备的接口,sink 节点表示匹配的 从设备接口。

Diplomacy 和 TileLink 使得设计硬件时可以运用下列设计模式更好地适应生成器为主的开发环境( generator-centric development environment)。

- DRYing Out Parameterization 利用参数化的方式避免了大量的重复

- Hardware Generation with A View 以大局观的方式生成硬件

- Correct By Composition 从构造方式上保证正确性

论文链接https://carrv.github.io/papers/cook-diplomacy-carrv2017.pdf

以下是论文中关于TileLink的介绍的中文翻译。

TileLink可以通过形式验证(formally-verifiable)来避免死锁,这得益于下列设计协议的决策:

- Generality of protocol interfaces 通用的协议接口

- Scalability rules for hierarchy 便于层次结构上可扩展的规则

- Strict prioritization of channels 通道之间严格的优先级

- Forward progress throughde coupled interfaces 通过解耦合的接口处理转发的过程

感谢林容威提供Abstract的翻译和介绍

RISC-V 工具链资料搜集

为了更好地统一RISC-V工具链的开发并和现有GCC参数保持一致,RISC-V的GitHub现在多了一个资料搜集工程。 其中罗列了一些现有文档和很多现有的编译参数,编译器自动生成的宏等等重要信息。

Spike Internal 文档

黄柏玮正在努力理解 Spike (RISC-V的指令集模拟器)内部实作,并将其整理成文档。其目的是让众多研究者和工程师针对模拟器及指令集做延伸时能更加容易从Spike 修改和模拟。最近,文档也将整合Evan Cox 所整理的 Spike reset/boot 的分析。阅读还在进行中,Spike 的代码也在不断更新 (譬如最近加上了Q扩展),因此阅读笔记也会适时更新。文档中如果出现错误,或者文档还没有覆盖的代码,也欢迎大家一起帮忙完成。

- 文档连结: https://github.com/poweihuang17/Documentation_Spike

- Evan Cox 关於 Spike boot/reset的整理:https://git.io/vFfqs

RISC-V toolchain中的Linker Relaxation(Palmer的 All aboard Part3)

在Part3中,接续着Linker重定位的讨论,Palmer向我们介绍了linker relaxation。有了重定位的概念後,relaxation其实蛮好懂的。在重定位时,我们会知道符号之间真正的距离,如果这个距离够近,我们就可以用另一种定址模式,这样会比较省指令和执行时间。举例来说,auipc+jalr 可以定址 32bit的范围,但jal却只能定址 21bit的范围。因此,在重定位时,一旦发现范围在 21bit以内,便可以换成 jal,省去一条指令。这个linker relaxation。

当然,除了jalr以外,还有很多地方,可以做relaxation。Palmer在这篇中有整理了几个给我们参考:

lui+addi有机会置换成 addi。auipc+jalr有机会置换成jal。- Relaxing Against the Global Pointer: 对於global variable的存取,比起用大量的

auipc,可以直接用一个寄存器gp,专门指向global variable存在的区域。这是一个”多寄存器 少定址模式” 的ISA中常用的技巧。MIPS中也有这样的设计。

看到这里,大家会发现,其实定址模式还蛮重要的。定址模式太多,会增加CPU设计的复杂度。定址模式太少或设计的不好,会让後续的变数存取变困难,而影响code size 和执行时间。以後小编有机会,会再带来 RISC-V 和其他 ISA 定址模式的比较。

- 更多细节可以参考Palmer的文章:http://t.cn/RWp0iAt

Chisel 的学习资料:Chisel Learning Journey

虽然Chisel跟RISC-V不直接相关,但因为Rocket和BOOM都是用Chisel写的,还是有不少人想透过学Chisel来更了解Rocket、BOOM 和 RISC-V。 Intensivate公司的Sean Halle 最近就组了个小组,一起编写了一份Chisel的tutorial,叫 Chisel Learning Journey。希望利用Sodor一步一步的带着大家先学会Chisel,再慢慢往Rocket和Boom中所使用的高阶功能迈进。有兴趣学Chisel的朋友可以参考参考。

- Chisel Learning Journey的连结:https://git.io/vFfqc

市场相关

Lauterbach 和 SiFive 一起发布了针对RISC-V IP的 TRACE32 Support

- 新闻连结:http://t.cn/RWoHP23

安路在最新发布的FPGA产品中支持RISC-V软核

国产FPGA厂商安路科技在最新推出的ELF2系列FPGA中表示其提供支持RISC-V软核。看来,越来越多的中国公司采用RISC-V了。

- 新闻连结:http://t.cn/RWoHhVz

CNRV社区活动

CNRV网站更新

- [3ac3e44] 加入Berkeley课程页CS61C

- [2c6dd26] 双周简报问卷调查结果分析

- [15df39a] 加入剑桥大学教学用处理器Clarvi

- [e7122bb] 加入黄柏玮逐步整理的Spike文档

- [c2f3eeb] 加入”Chisel Learning Journey”: 一个关于学习Chisel的资料搜集wiki

- [628f063] 加入维基百科上的RISC-V词条

- [3006f4d] RISC-V 工具链资料搜集页面

暴走事件

十一月

- BSDTW17 2017年11月11-12日,BSDTW17会有两场关于RISC-V的演讲,地点在台北。

- The 7th RISC-V workshop 2017年11月28-30日,第7届RISC-V研讨会将在美国加州Milpitas由西部数据承办。

招聘简讯

CNRV提供为行业公司提供公益性质的一句话的招聘信息发布,若有任何体系结构、IC设计、软件开发的招聘信息,欢迎联系我们!

整理编集: 宋威、黄柏玮、郭雄飞

贡献者: 王翔、林容威

欢迎关注微信公众号CNRV,接收最新最时尚的RISC-V讯息!

本作品采用知识共享署名-非商业性使用-相同方式共享 3.0 中国大陆许可协议进行许可。