CNRV

关注RISC-V和Chisel以及开源IC和EDA在中国的发展

RISC-V 双周简报 (2017-08-03)

RV新闻

RISC-V教育专题邮件列表成立

Krste Asanovic正式宣布设立独立的RISC-V教育专题邮件列表: RISC-V Teach

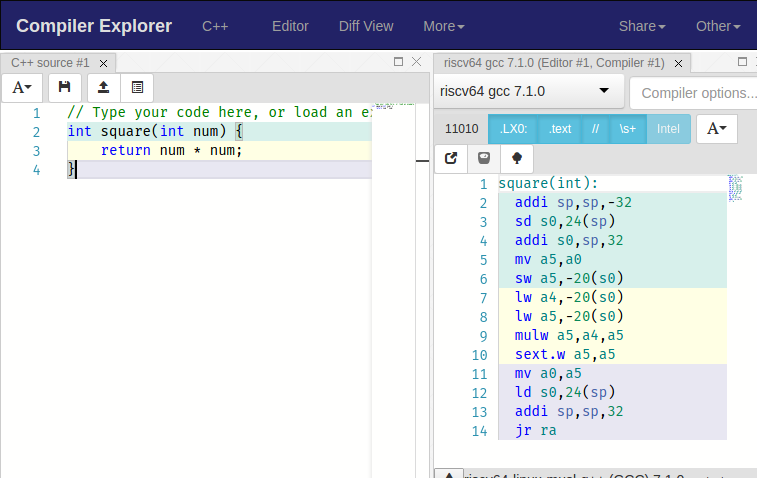

RISC-V版Compiler Explorer

Michael Clark,rv8二进制解释执行器的作者,将RISC-V的GNU GCC7.1编译器加入了Compiler Explorer的支持中。 Compiler Explorer是一个在线的编译器,可以将一小段代码编译成汇编代码并很友好地显示在同一个页面中,十分有利于理解编译器的编译结果。 现在的版本架在Michael Clark自己的AWS云中,可以从这里访问:https://cx.rv8.io。感兴趣的同学不如尝试一下。

RISC-V中文书

正在筹划中RISC-V中文书:《关于RISC-V你所需要知道的一切》 正在积极筹备中。现在已基本确定前4章的主要内容。希望RISC-V的爱好者们贡献力量一起来写这本书。(书籍的License目前定位CC-By-NC-SA)

Linux porting patch 第七版

虽然错过了4.13,但 Palmer 仍然继续在改善linux port。最近他提交了第七版,同时也提到下一步是希望能尽快进入linux-next。

newlib/libgloss/libm patch

最近,newlib/libgloss/libm 的 RISC-V patch 开始被review了。期待它能早日通过。

B 小组重启

Rex McCrary 在 isa-dev 上向大家宣布了 B 小组重启的消息。期待他们能设计出好的B extension。

Hackaday: VexRiscv: A Modular RISC-V Implementation for FPGA

Hackaday介绍了一个新的RISC-V CPU实现: VexRiscv,重点是这个CPU是用另一种高层描述语言SpinalHDL描述的,SpinalHDL也是基于Scala设计的一种DSL.

Since an FPGA is just a sea of digital logic components on a chip, it isn’t uncommon to build a CPU using at least part of the FPGA’s circuitry. VexRiscv is an implementation of the RISC-V CPU architecture using a language called SpinalHDL.

SpinalHDL is a high-level language conceptually similar to Verilog or VHDL and can compile to Verilog or VHDL, so it should be compatible with most tool chains. VexRiscv shows off well in this project since it is very modular. You can add instructions, an MMU, JTAG debugging, caches and more.

…

Github: https://github.com/SpinalHDL/VexRiscv

EETime: Hot Chips Gets More Diverse

An IoT session will include the first of two talks on RISC-V, the open-source CPU architecture spurring lots of interest. We’ll hear about an SoC from SiFive and later that day an open source fabric for accelerators.

…

详见暴走事件

技术讨论

多中断时的响应顺序

如果多个中断同时到来,一个是机器(machine)态的中断源但是会被转移(delegate)到用户(user)态响应,另一个是系统(supervisor)态的中断,哪一个会被先响应呢?

回答是:系统中断会被先响应。机器中断可能被先响应,然后被转移到用户态,这时候系统态的优先级比用户态高,于是发生中断抢占,结果还是系统中断被先响应。Privilege spec将加上这样的解释:

Multiple simultaneous interrupts destined for different privilege modes are handled in decreasing order of destined privilege mode. Multiple simultaneous interrupts destined for the same privilege mode are handled in the following decreasing priority order: MEI, SEI, UEI, MSI, SSI, USI, MTI, STI, UTI. Synchronous exceptions are of lower priority than all interrupts.

Link: https://goo.gl/4rj1hp

原子操作(atomic operation)与临界区(critical section)

这是一个老话题,但最近又被重新提起。

RISC-V为什么建议使用LL/SC(load lock and store check)来实现临界区而不使用CAS(compare and swap)的原子操作来实现呢?

CAS不能很好地处理ABA问题。LL/SC机制能够保证硬件锁没有被写过,即使是写成同样的值。

In multithreaded computing, the ABA problem occurs during synchronization, when a location is read twice, has the same value for both reads, and “value is the same” is used to indicate “nothing has changed”. However, another thread can execute between the two reads and change the value, do other work, then change the value back, thus fooling the first thread into thinking “nothing has changed” even though the second thread did work that violates that assumption.

From Wikipedia

Github Issue: https://git.io/v72so

原子操作能在微实现中替换成两个微操作吗?

这样是很危险的。如果在微操作过程成出现中断等等跳转,原子操作的原子性就被打破了。

Link: https://goo.gl/XrwiiB

直接缓存操作(explicit cache control)指令提案(第3版, 第4版)

提示:这仅是对RISC-V指令扩展的提案,不代表提议已被接纳

Jacob Bachmeyer 又提出了直接缓存操作指令的第3版。

直接缓存操作指令扩展了FENCE指令还未用的指令空间。

其主要的功能包括:

- FENCE(有的架构也叫barrier)

- FENCE.I 原有的指令fence

- FENCE.RD 带区间的数据fence

- FENCE.RI 带区间的指令fence

- 预取

- MEM.PF(0-3) 在L0至L3预取数据 - MEM.PF.EXCL 预取数据并获得可写权限

- MEM.PF.ONCE 欲取数据并暗示只读一次(assistant cache)

- MEM.PF.TEXT 预取指令

- 缓存锁定(把部分缓存的区域变成scratchpad)

- CACHE.PIN 锁定数据区域

- CACHE.UNPIN 解锁数据区域

- CACHE.PIN.I 锁定指令区域

- CACHE.UNPIN.I 解锁指令区域

- 缓存清理(flush)

- CACHE.WRITEBACK 强制写回缓冲区域(但不失效)

- CACHE.FLUSH 清除缓冲区域(写回并失效)

- 其他破坏性缓存操作

- MEM.DISCARD 直接失效缓存区域(数据丢失,用于抛弃无用数据而避免写回)

- MEM.REWRITE 为写操作直接初始化缓存区域而不读取数据(已知数据会被彻底覆盖时,可以直接创建缓存数据同时标记已修改)

具体的讨论可着重看这么几段:

- 第3版初始提议 Link: https://goo.gl/PRavjZ

- Allen Baum的总结 Link: https://goo.gl/8kWY3Y

- 第4版初始提议 Link: https://goo.gl/HcXN1H

其中MEM.REWRITE操作较难理解。一个较简单的例子是考虑一个处理器做DMA或者清除一大片数据区域,在已知数据区域会被完全重写覆盖时,由于coherence引起的数据同步是无意义的数据传输。只需要获得写入权利然后清除数据即可。

代码更新

Rocket-chip阅读笔记

宋威正在努力理解最新的Rocket-chip源码。其目的是让lowRISC使用最新的Rocket处理器,从而支持priv 1.10,断点调试,中断配置等等。在阅读的同时,也将对Rocket-chip代码的分析整理成文档。阅读还在进行中,Rocket-chip的代码也在不断更新,阅读笔记也会适时更新。笔记中如果出现错误,或者笔记还没有覆盖的代码,希望大家能帮忙一起完成。

Github Repo: https://git.io/v72sE

Rocket-chip代码结构调整

Freechipsproject/rocket-chip经历了一次较大的结构调整。 其中包括:

- 更名和合并原有总线至sbus, pbus, ibus和memBuses。

- 重定义Tile的代码封装。

- DTS(device tree)归入BaseCoreplex。

- 外设默认设置并入BaseCoreplexConfig。

(hcook)

Combine Coreplex and System Module Hierarchies:

- RocketCoreplex is now extended by ExampleRocketTop to create the top-level module

- L1toL2 network and systemBus are now sbus

- coreplexBus and peripheralBus are now pbus

- intBus and int_xbar are now ibus

- mem is now memBuses

- Peripheral devices attach to pbus and ibususing traits in the devices package

- External ports now attach to sbus using traits in the coreplex package

- New wrapper classes RocketTileWrapper and TLBusWrapper

- DTS functionality handled in BaseCoreplex

- BaseCoreplexConfig contains default peripheral settings

GitHub PR: https://git.io/v72sa

暴走事件

八月

- RISC-V at HotChips, 20-22 August 2017 at Cupertino, California.

十月

- OSDT开源开发工具大会2017(也就是原HelloGCC会议)将在10月下旬在北京举办,话题和赞助征集已经开始。话题内容包括“面向RISCV等新硬件的基础软件支持”,各位不要错过。

- 开源经济学研究-2017年年会邀请函

- RISC-V at the Linley Processor Conference, 4-5 October 2017 at Santa Clara, California.

- First Workshop on Computer Architecture Research with RISC-V (CARRV 2017), 14 October at Boston, Massachusetts, co-located with MICRO 2017.

招聘简讯

CNRV提供为行业公司提供公益性质的一句话的招聘信息发布,若有任何体系结构、IC设计、软件开发的招聘信息,欢迎联系我们!

整理编集: 宋威,郭雄飞,黄柏玮

欢迎关注微信公众号CNRV,接收最新最时尚的RISC-V讯息!

本作品采用知识共享署名-非商业性使用-相同方式共享 3.0 中国大陆许可协议进行许可。